一、说明

本文以Universal Serial Bus Specification Revision 2.0 April 27, 2000内容为准。

USB2.0支持三种速率,High speed(480Mb/s±500ppm)、Full speed(12Mb/s±2500ppm)以及Low speed(1.5Mb/s±1.5%);

USB2.0支持三种模式,Host、Device以及Hub;

USB2.0使用NRZI编码技术,这种编码方式基于非归零的原则,即在信号的每个位期间,如果位为1,则电平保持不变,如果位为0,则电平发生反转。这种编码方式集成了RZ编码和NRZ编码的优点,既能传输时钟信号,又能尽量不损失系统带宽,如下图所示。

USB2.0共有4根线,可以传输数据和电源,如下图:

二、电气参数

测量环境要求:20℃

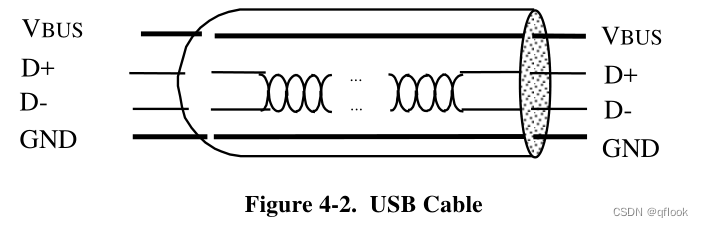

1.线材

操作温度范围:0~50℃

存储温度范围:-20~60℃

直流阻抗:<0.6Ω

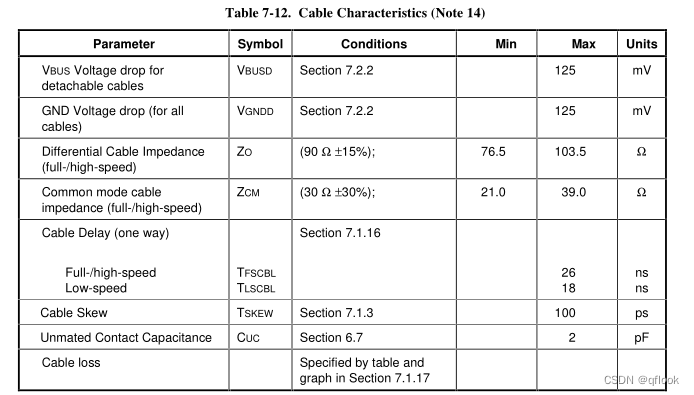

D+和D-之间偏差skew不能超过100ps;

以及协议文档也规定了可靠性、安全类具体指标,具体参考协议,本文不再赘述;

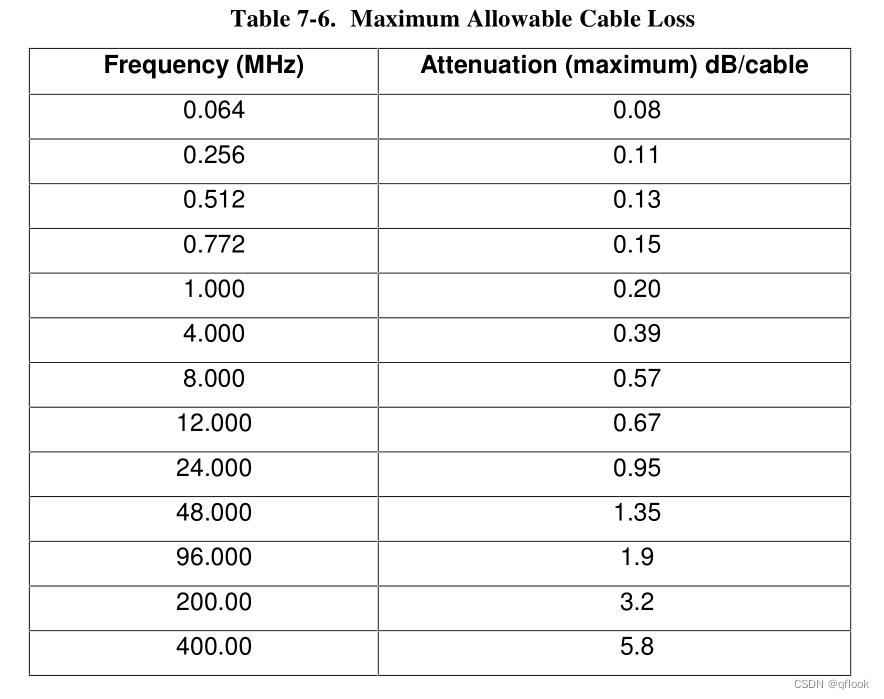

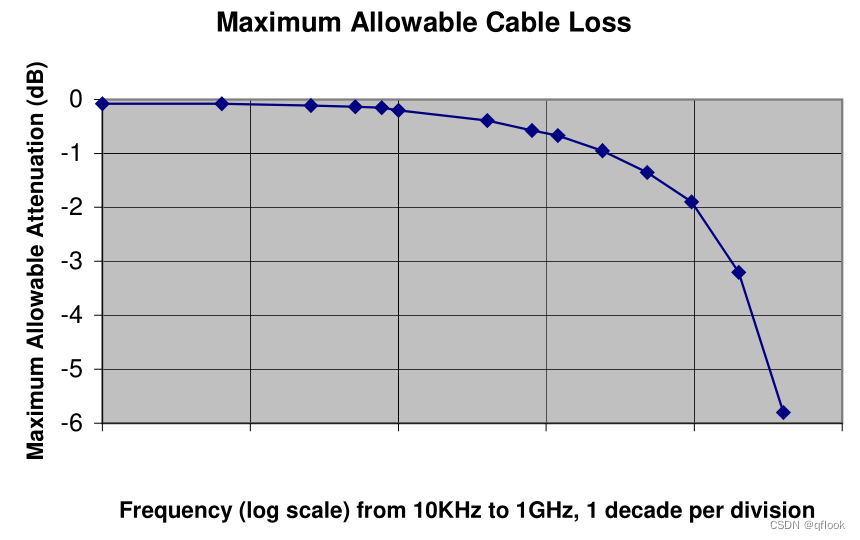

线材的衰减要求如下:

图形化如下图:

2.TX 参数要求

2.TX 参数要求

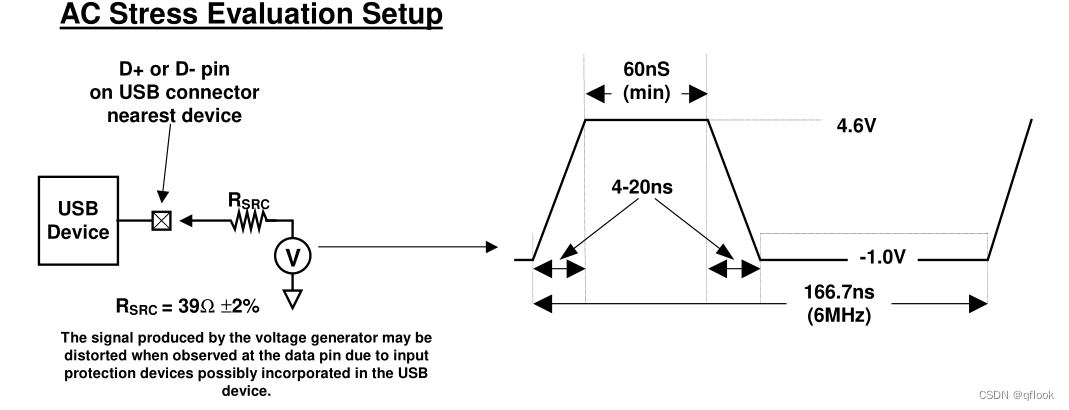

低速和全速模式,在开路情况下最坏输出的过冲和下冲是4.6V和-1V,如下图:

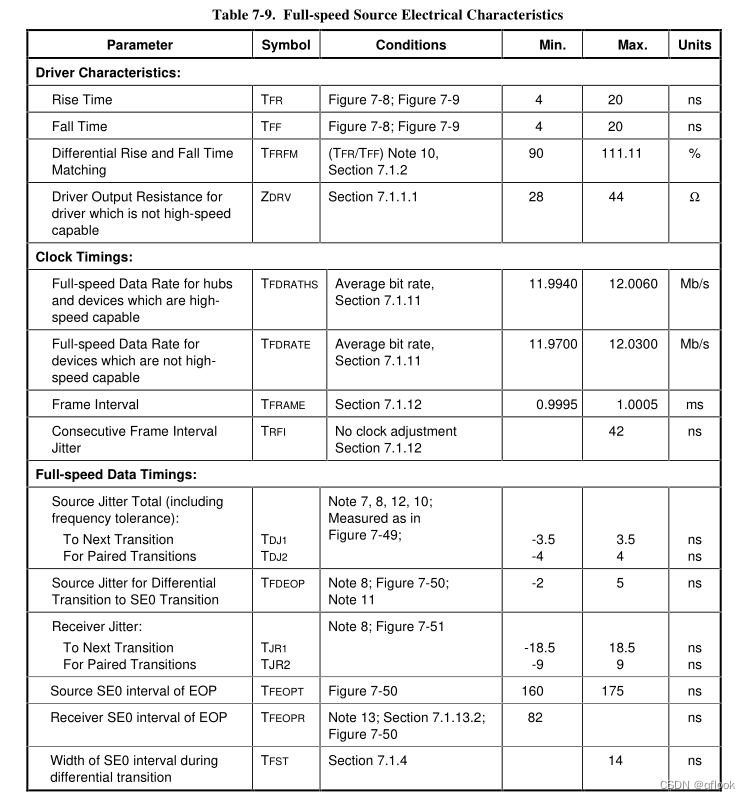

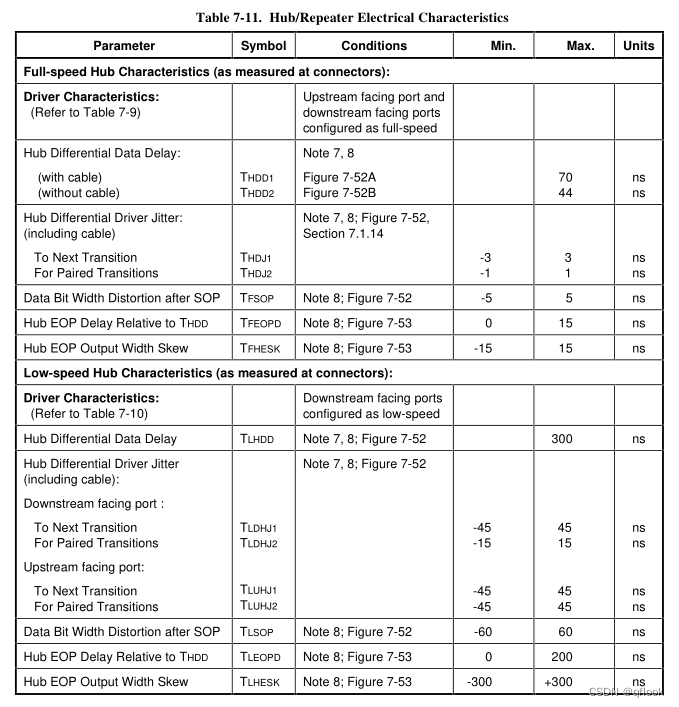

1)Full speed全速模式

线材:差分阻抗范围是90±15%Ω,共模阻抗是30±30%Ω,最大延迟26ns。

driver阻抗:当全速driver不是高速driver的一部分时,要求driver阻抗28~44Ω;当其是高速driver的一部分时,要求阻抗40.5~49.5Ω;

输出电平:输出低电平VOL≤0.3V(通过1.5kΩ电阻上拉到3.6V电源),输出高电平VOH≥2.8V(下拉电阻15kΩ)

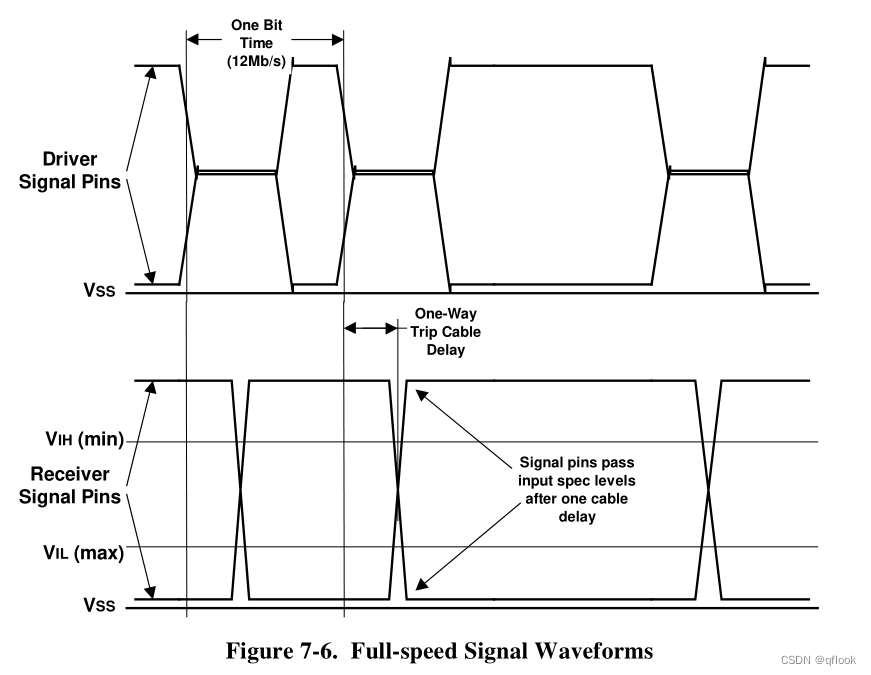

全速信号波形图:

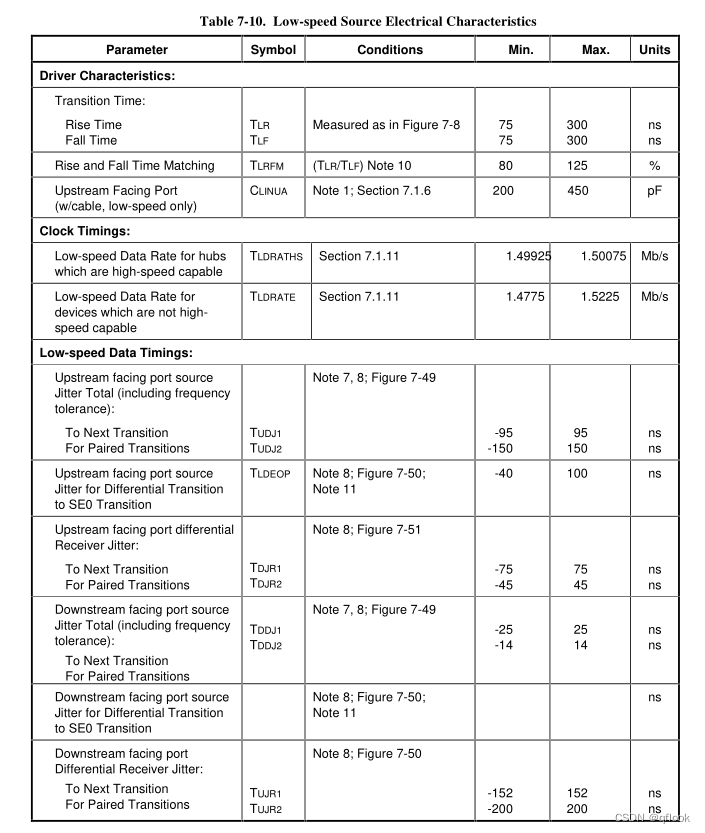

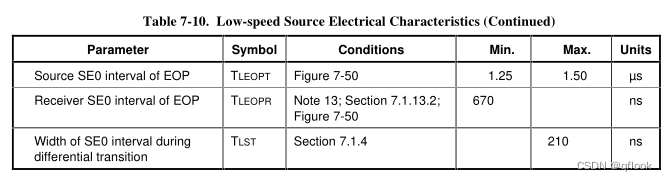

2)Low speed低速模式

2)Low speed低速模式

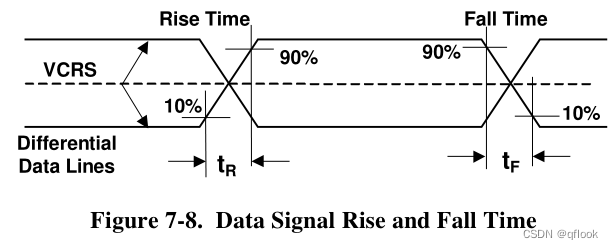

线材:单端电容≤200pf,D+和D-间电容≤450pf,延迟≤18ns;

输出电平:输出低电平VOL≤0.3V(通过1.5kΩ电阻上拉到3.6V电源),输出高电平VOH≥2.8V(下拉电阻15kΩ)

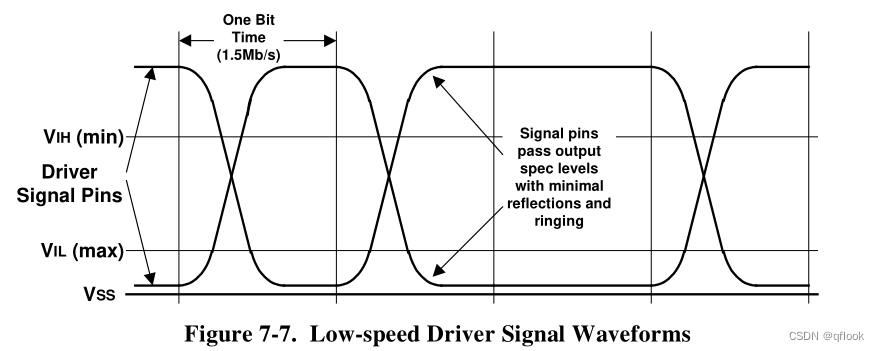

低速信号波形图:

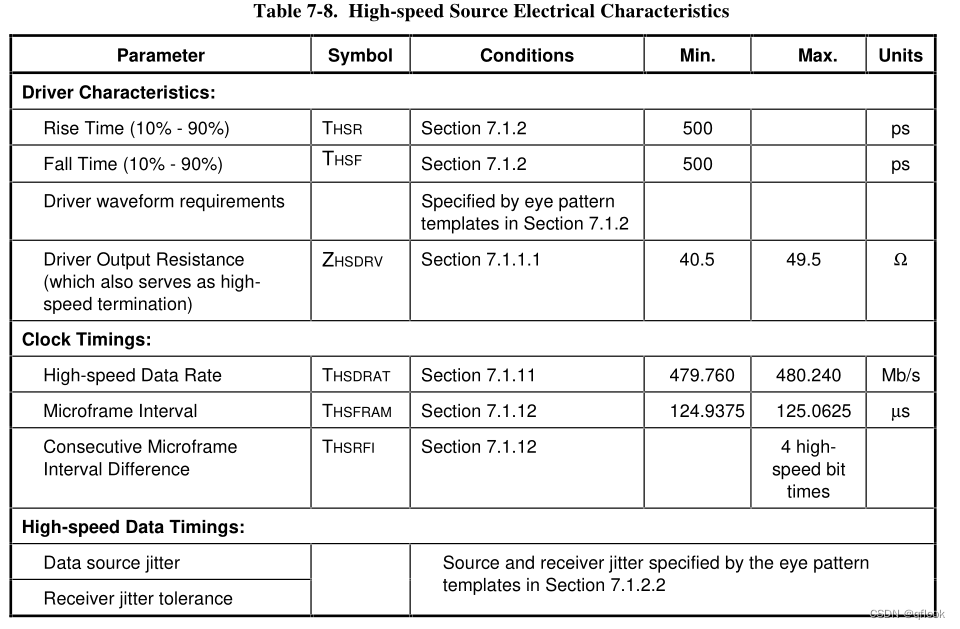

3)High speed高速模式

线材:要求和全速模式相同,

driver阻抗:输出阻抗90±10%Ω;

输出电平:输出高电平VHSOH范围400±10%mV,低电平VHSOL范围0±10mV;

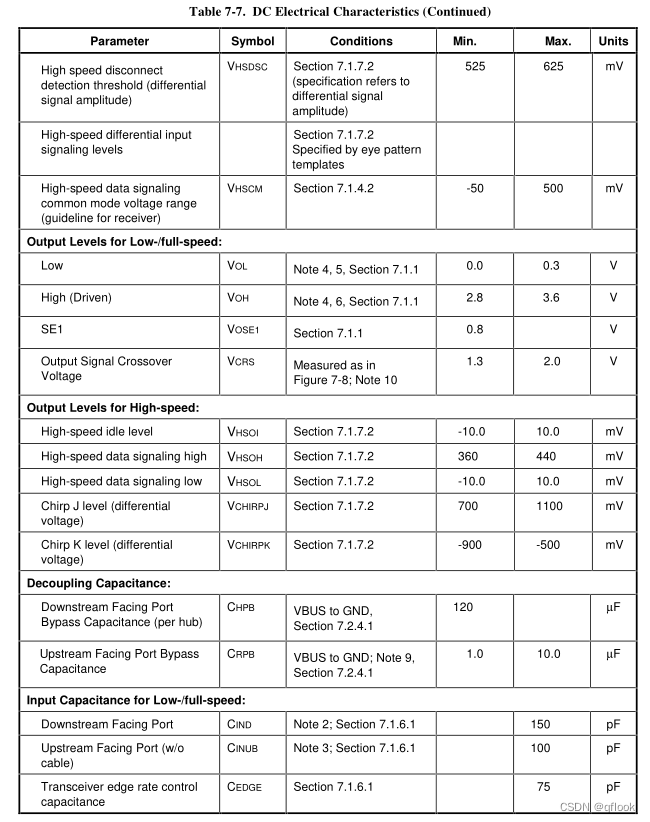

汇总表格如下:

| 模式 | 线材 | driver | 输出电平 |

| 低速 | 单端电容≤200pf,D+和D-间电容≤450pf,延迟≤18ns | / | VOL:【0~0.3V】 VOH:【2.8~3.6V】 |

| 全速 | 差分阻抗范围是90±15%Ω,共模阻抗是30±30%Ω,最大延迟26ns | 支持HS:40.5~49.5Ω 不支持HS:28~44Ω | |

| 高速 | 90±10%Ω | VHSOH:400±10%mV VHSOL:0±10mV |

以及,在全速和低速模式下,信号交叉电压VCRS的范围是1.3~2V之间。

3.上升下降时间及眼图要求

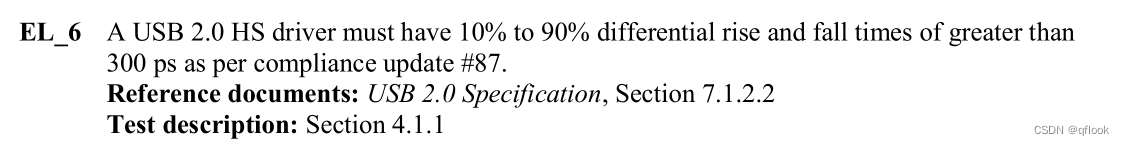

在高速模式下,上升下降时间(10%~90%)协议要求>500ps(在汇总电气参数图中有明确要求),但是官方测试文档要求>300ps,不确定是否写错了?

在全速模式下,上升下降时间(10%~90%)范围是4~20ns,且TF和TR差别在10%以内;

在低速模式下,上升下降时间(10%~90%)范围是75~300ns,且TF和TR差别在20%以内,如下图:

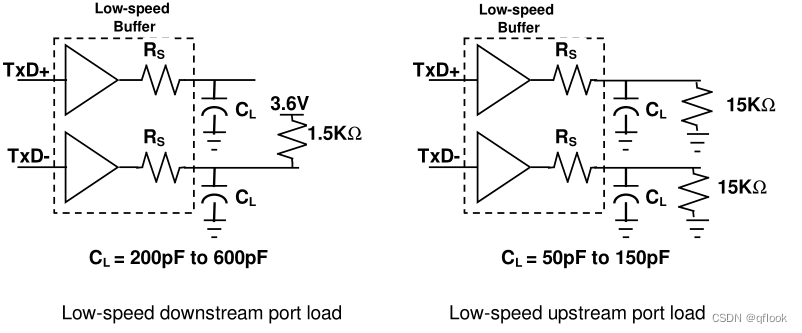

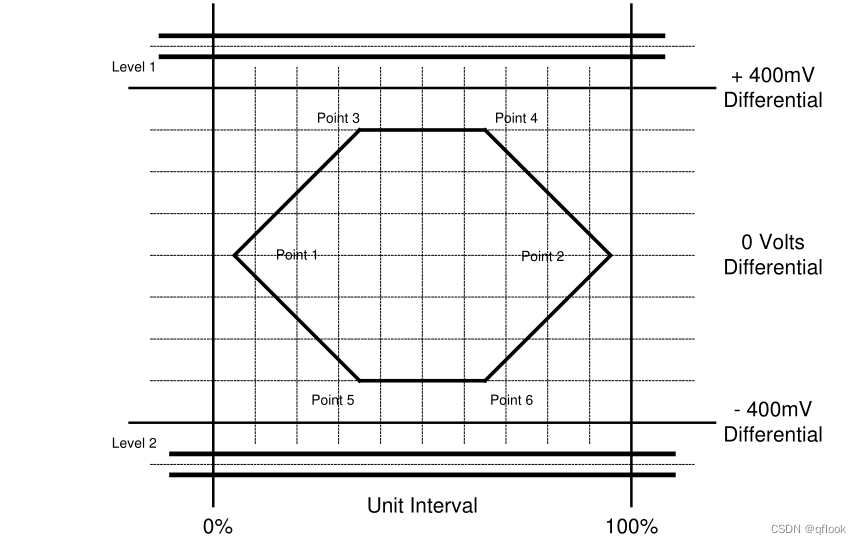

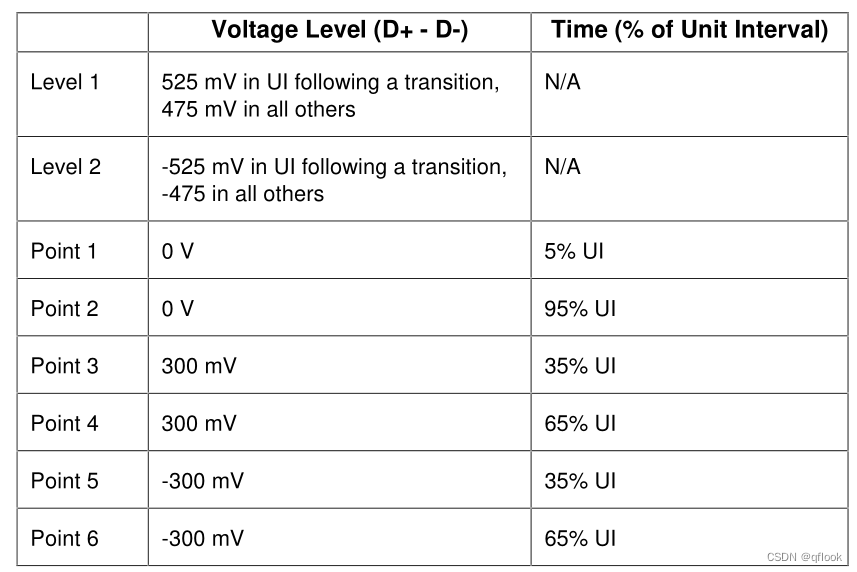

眼图模板较多,首先看下TP点,如下图:

眼图模板较多,首先看下TP点,如下图:

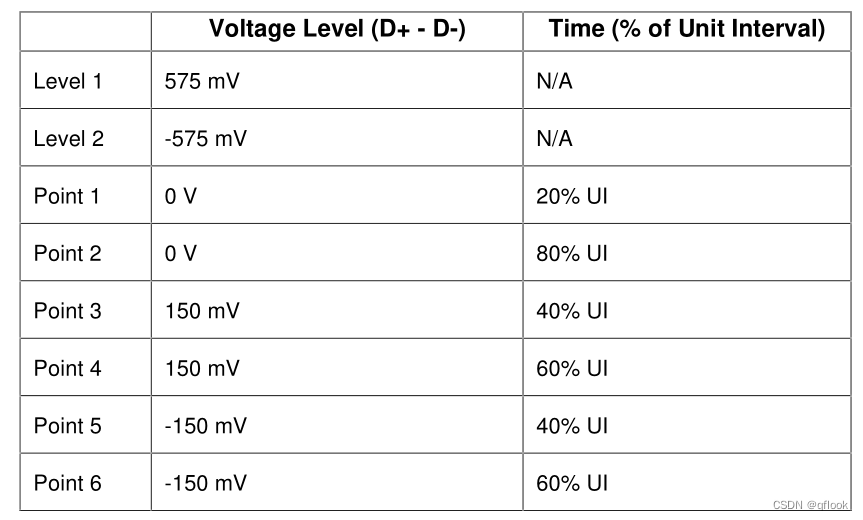

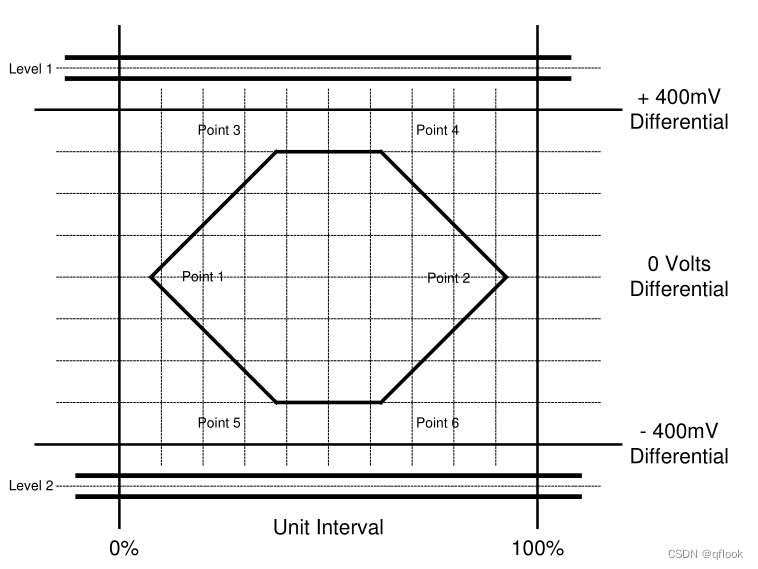

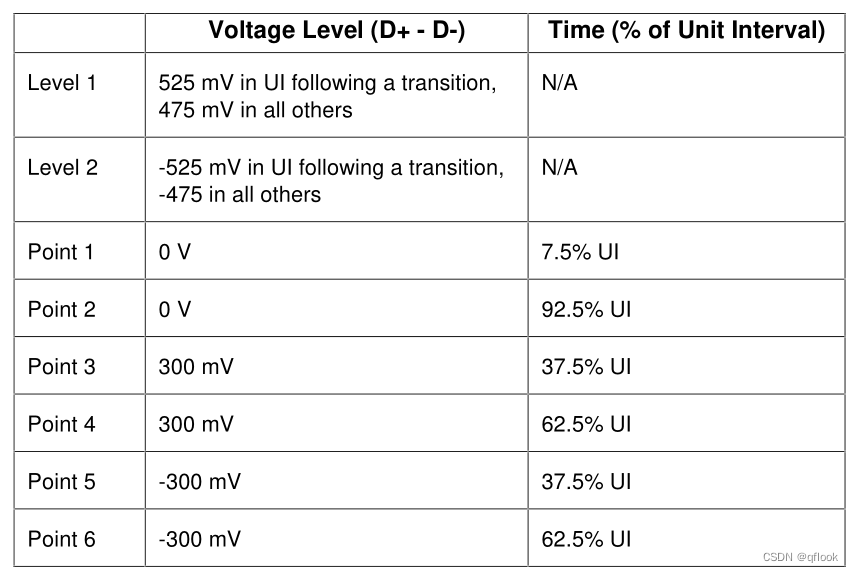

模板1,协议要求适用于Hub的TP2和Device的TP3,但是官方测试规范上Host的TP2也是适用本模板。在一致性测试软件是Near近端的眼图就是这个。

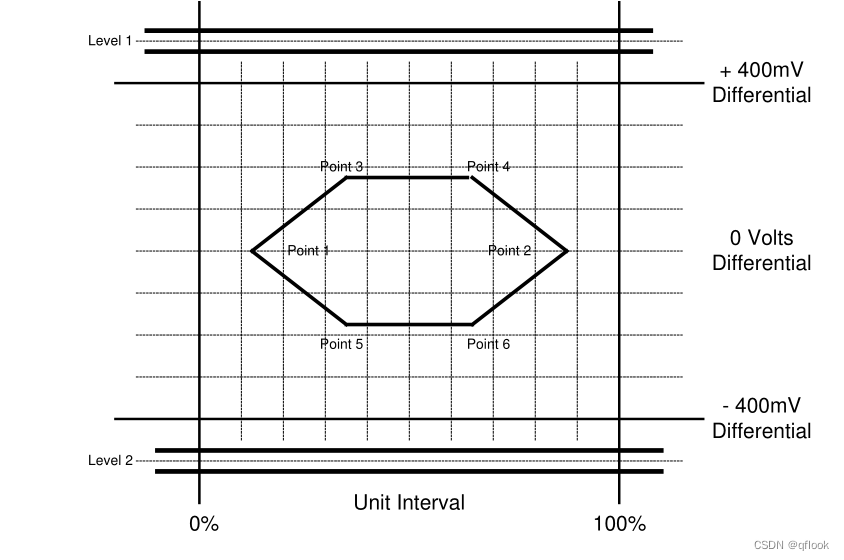

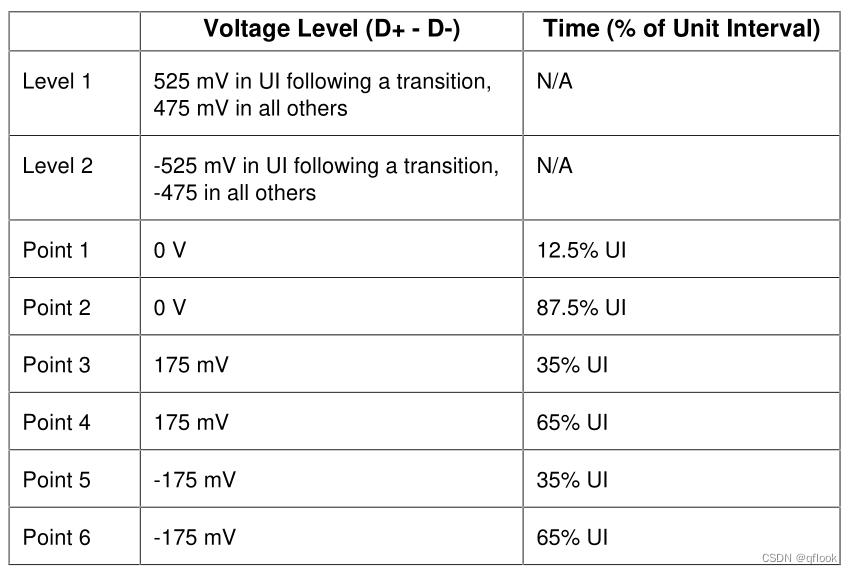

模板2,Device的TP2点,也就是带线传输后的眼图要求,官方测试规范指出Hub和Host的TP3也适用本模板。在一致性测试软件中的Far远端的眼图就是这个。

模板2,Device的TP2点,也就是带线传输后的眼图要求,官方测试规范指出Hub和Host的TP3也适用本模板。在一致性测试软件中的Far远端的眼图就是这个。

模板3和模板4是测试接收灵敏度信号的要求,忽略;

模板5,适用于Host和Hub的TP1,以及Device的TP4,也就是测试芯片输出管脚处的眼图模板。

模板6,适用于Host和Hub的TP4,以及Device的TP1,也就是测试芯片输入管脚处的眼图模板。

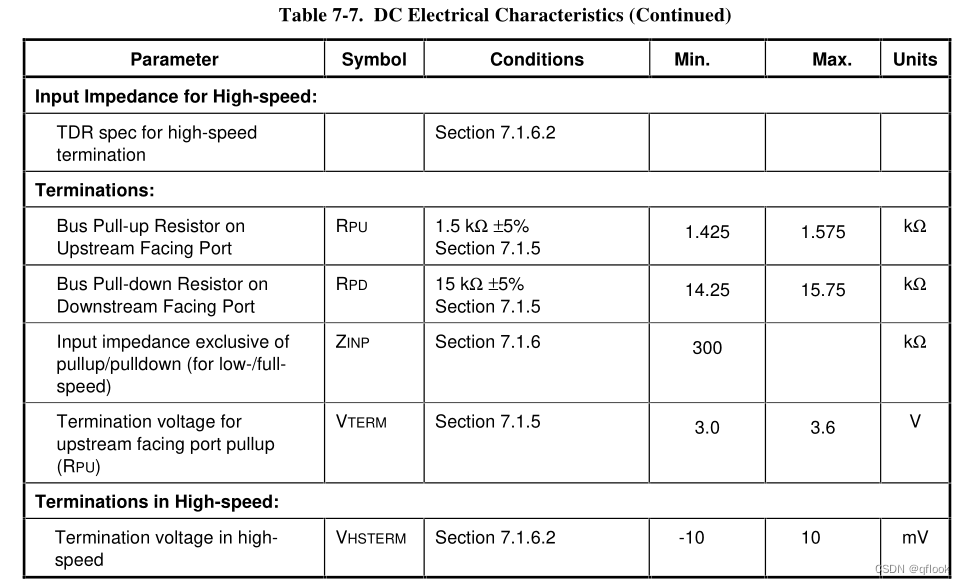

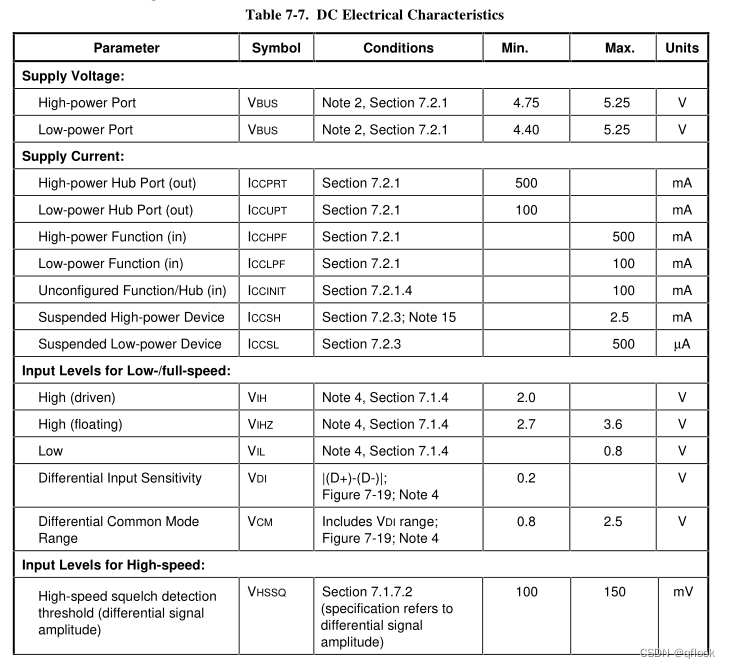

4.RX参数要求

1)低速和全速模式,差分共模VCM的范围是0.8~2.5V;差分输入灵敏度VDI≥200mV;单端信号VIH≥2V,VIL≤0.8V;

在差分信号状态转换过冲中,D+和D-可能出现同时低于VIH的现象,协议要求低速模式≤210ns,全速模式≤14ns;

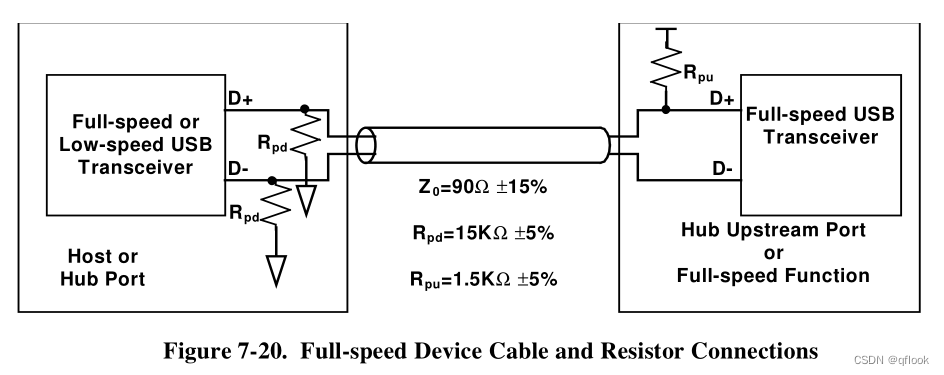

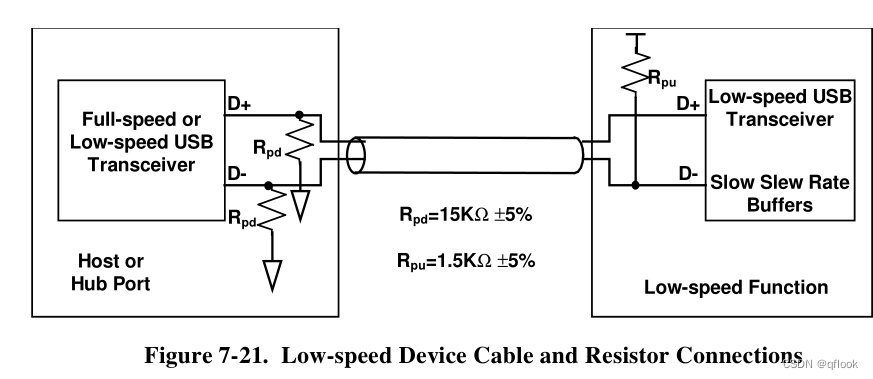

全速和低速的识别是通过数据线的上拉选择来实现的,D+使用1.5K电阻上拉则是全速模式,D-上拉则是低速模式(个人理解应该是上下拉电阻分压,然后识别不同数据线的电平来实现的),如下图:

至于高速模式的识别,就需要握手协议了,发送KJ码来切换到高速模式,高速模式下信号电平就关断上拉电阻进入阻抗匹配的模式,幅值也会变成400mV的高速JK码了。

至于高速模式的识别,就需要握手协议了,发送KJ码来切换到高速模式,高速模式下信号电平就关断上拉电阻进入阻抗匹配的模式,幅值也会变成400mV的高速JK码了。

高速模式,差分共模VHSCM的范围是-50~500mV,典型值是200mV;

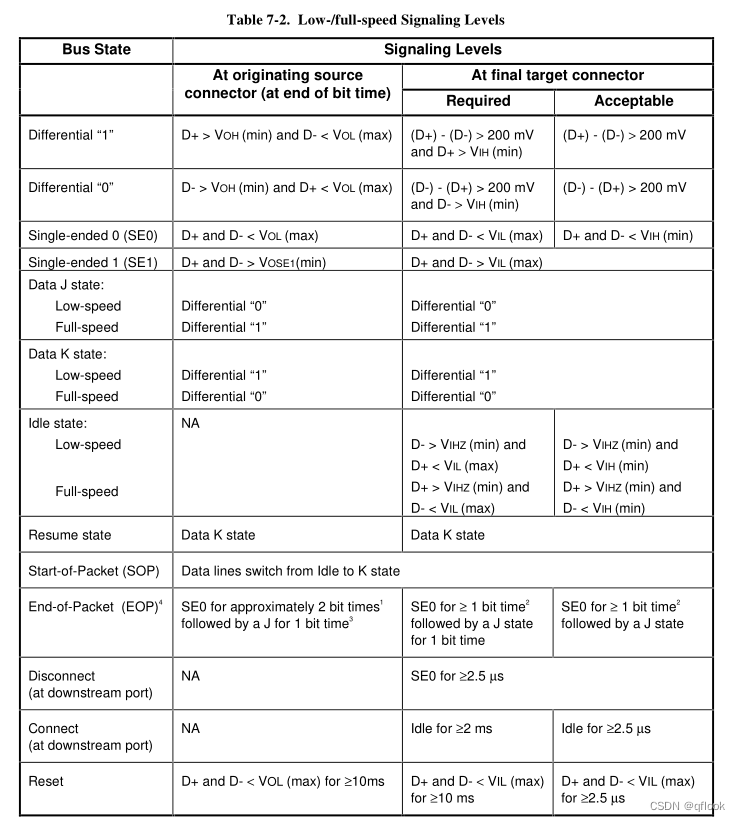

5.信号level

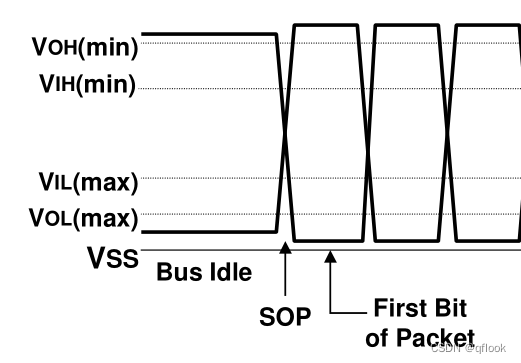

低速和全速信号的要求如下图,其中低速J码是差分0,K码是差分1;全速J码是差分1,K码是差分0,正好相反。SE0也就是单端信号0,代表D+和D-都是0电平;SE1也就是单端信号1,代表D+和D-都是1电平;总线空闲状态,低速模式D+是0,D-是1,也就是低速J码;全速模式D+是1,D-是0,也就是高速J码;表中还有reset时序要求总线在SE0状态下持续时间最好不少于10ms,不少于2.5us也是可接受的。

SOP是空闲状态切换到K码;EOP是至少1bit时长的SE0+J码,持续时长要求低速模式1.25~1.5us,全速模式160~175ns;

注意第二列是开始输出的要求,第三列是接收端必须的要求,最后一列是接收端可接受的要求;

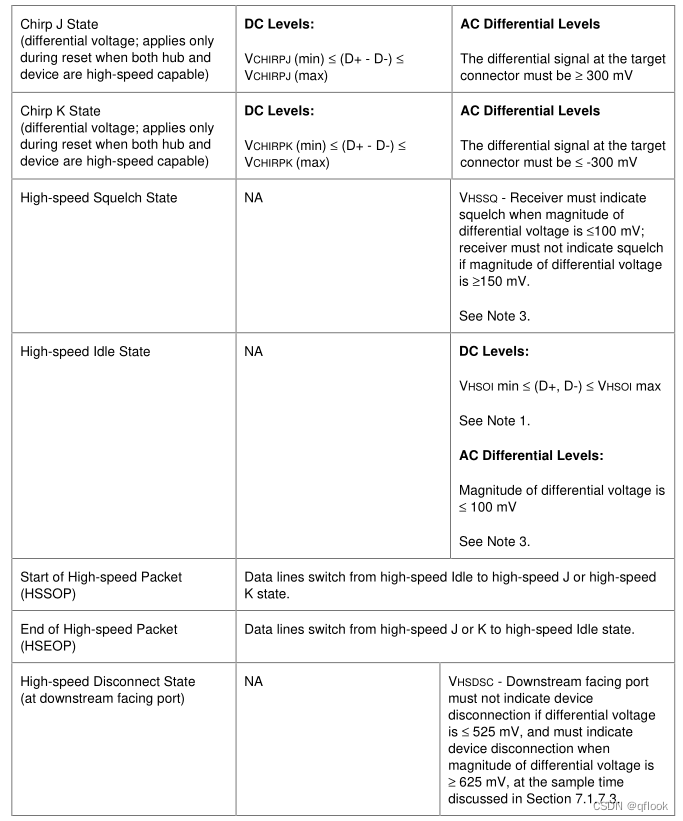

高速信号level要求如下图,其中JK码和全速定义相同,需要注意高速模式SOP的定义是总线空闲切好的J或K码,EOP定义是K或J码切换到空闲;Chirp J/K码只用于握手过程中,无需特别关注;高速模式的总线空闲状态,需要D+和D-都是0,也就是总线处于SE0状态。

高速信号level要求如下图,其中JK码和全速定义相同,需要注意高速模式SOP的定义是总线空闲切好的J或K码,EOP定义是K或J码切换到空闲;Chirp J/K码只用于握手过程中,无需特别关注;高速模式的总线空闲状态,需要D+和D-都是0,也就是总线处于SE0状态。

特别注意,SOP是状态切换,如下低速/全速的示意图:

特别注意,SOP是状态切换,如下低速/全速的示意图:

网分需要设置上升时间为400ps;

终端匹配阻抗Termination Impedance (Z HSTERM ) ,typeA接口需要延长8ns的线材,typeB接口需要延长4ns的线材;判断标准是80~100Ω。

通过阻抗Through Impedance (Z HSTHRU )是指连接器参考位置前500ps到受终端电阻影响的位置,判断标准是70~101Ω;

7.电气参数汇总

说明:Low-Power Port是指低功耗Hub(仅有一个负载),Vbus可以最低4.4V,其他情况最低电压4.75V;

三、测试模式

Test_se0_nak模式,这个模式下DUT进入高速接收模式,主要用来进行测试输出阻抗、低电平输出电压和负载相关参数;

Test_J模式,该模式下DUT进入高速模式J码状态,D+输出高电平;

Test_K模式,该模式下DUT进入高速K码状态,D-输出高电平;

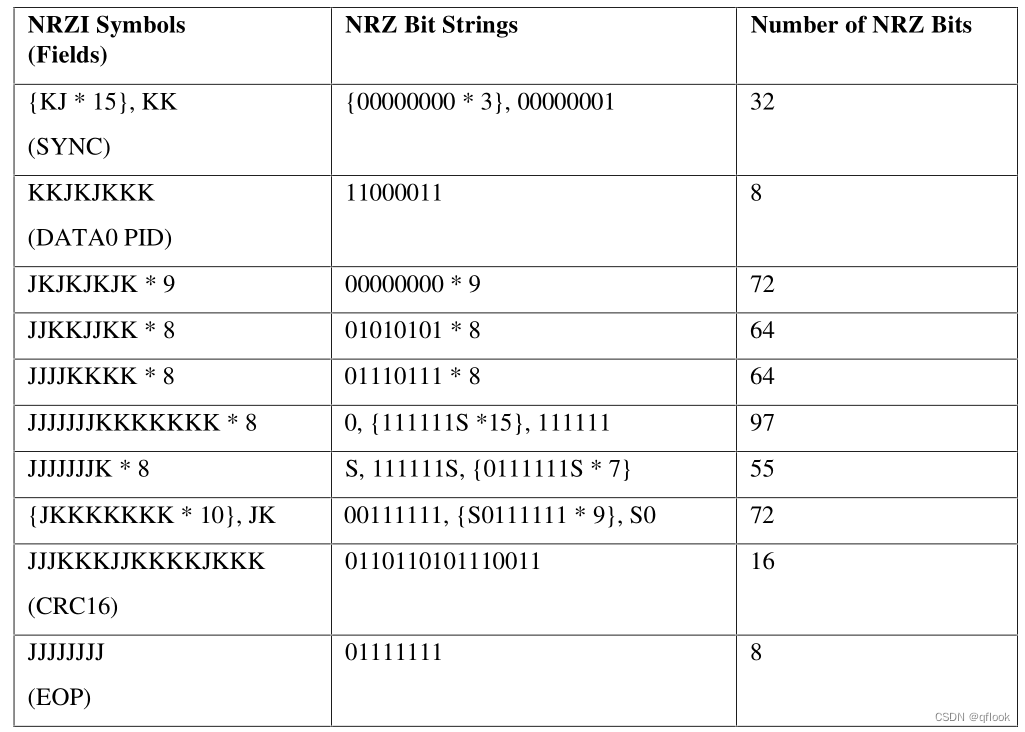

Test_Packet模式,本模式下主要进行上升/下降时间测试、眼图测试、抖动及其他动态参数的测试等。一致性测试就是进入本模式。

测试包具体内容是:

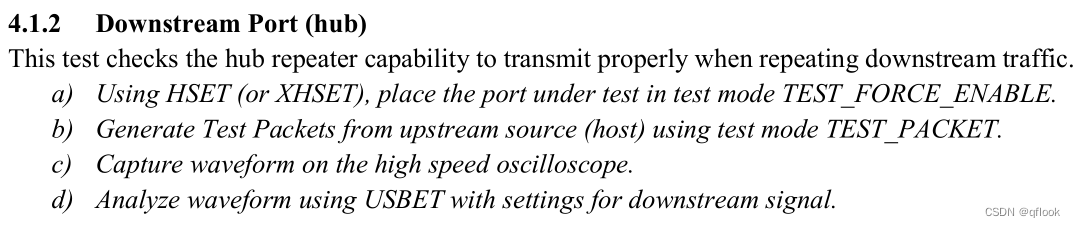

Test_Force_Enable模式,该模式一般测带Hub的环境,配合其他模式一起进行测试。例如:

四、最后

就写到这吧,其他协议层等属于软件需要了解的东西了。简单看了下,本文总结的有点乱,有两个原因吧,其一是理解的不够透彻,无法用简单明了的语言总结;其二是感觉这个协议文档章节划分的也不是很好,有点大杂烩。

水平有限,肯定有错误的地方,希望大家可以指正出来,感谢。